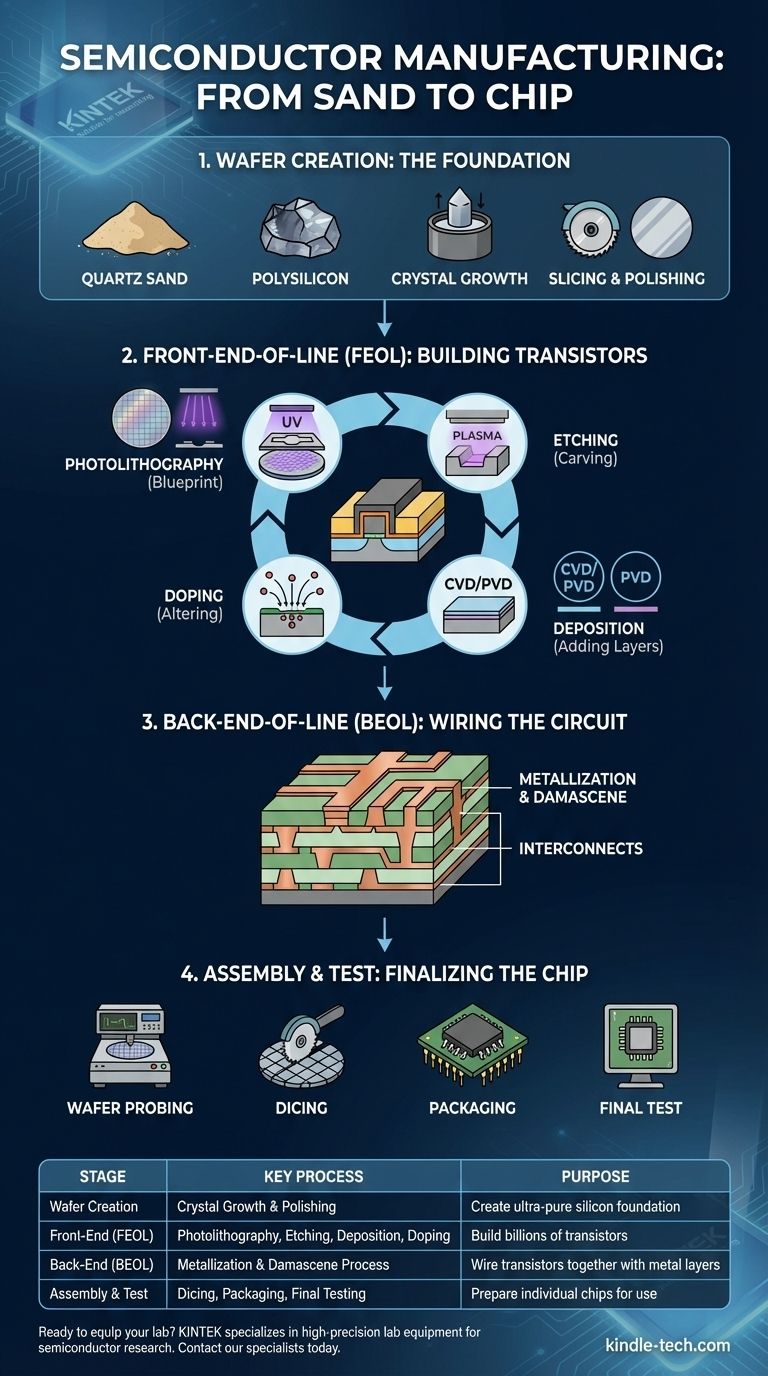

从核心来看,半导体制造是在纯硅晶圆上构建一个由数十亿个电子开关组成的微观城市的过程。 这并非单一动作,而是一个高度受控的、由数百个不同步骤组成的序列,大致分为四个主要阶段:制造硅晶圆、在晶圆上制造电路(前端)、将这些电路连接起来(后端),最后是测试和封装成品芯片。每个阶段都需要极高的精度,这在所有现代工业中都是要求最高的。

需要掌握的核心概念是,芯片制造是一个加法和减法过程的迭代循环。材料层(有时只有原子厚度)被精心沉积到硅晶圆上,使用光进行图案化,然后选择性地刻蚀掉,以逐渐形成构成现代集成电路的数十亿个晶体管。

从沙子到硅:制造晶圆

在制造任何电路之前,基础必须是完美的。这个基础就是一块几乎完美无瑕、超纯的硅圆盘,称为晶圆。

原材料:多晶硅

该过程始于石英砂(二氧化硅),通过加热和提纯生产出冶金级硅。然后将其进一步精炼成电子级多晶硅,这是一种纯度达到99.9999999%的材料。这种极高的纯度是不可妥协的,因为即使是微小的杂质也可能破坏芯片的电学性能。

生长晶锭

将多晶硅在坩埚中熔化。将一小块籽晶浸入熔融硅中,并缓慢向上拉起,同时旋转。随着拉起,熔融硅冷却并凝固,遵循籽晶的晶体结构。这形成了一个大的单晶圆柱体,称为晶锭或“晶棒”,其长度可超过两米,重量可达数百公斤。

切割和抛光

然后使用金刚石锯将圆柱形晶锭切割成非常薄的圆盘。这些原始圆盘,称为晶圆,经过研磨和抛光,形成镜面般无缺陷的表面。典型的晶圆厚度不到一毫米,但必须绝对平坦。

芯片制造的核心:前端工艺 (FEOL)

这是在硅晶圆表面直接构建晶体管(芯片的基本开关)的地方。这通过四个关键过程的重复循环实现。

步骤1:光刻(蓝图)

光刻是芯片制造中最关键的步骤。将一层光敏材料,称为光刻胶,涂覆在晶圆上。一个掩模,其作用类似于包含电路某一层蓝图的模板,放置在晶圆上方。然后通过掩模投射特定波长的光(通常是深紫外线,或DUV/EUV),改变曝光区域光刻胶的化学结构。

步骤2:刻蚀(雕刻图案)

然后将晶圆暴露在化学品或等离子体中,去除软化的光刻胶。这留下了一层图案化的硬化光刻胶,保护了晶圆的某些区域,同时暴露了其他区域。在刻蚀过程中,使用气体(干法刻蚀)或液体(湿法刻蚀)从暴露区域去除材料,将电路图案刻蚀到下层。

步骤3:沉积(添加新层)

刻蚀后,新的材料层被添加到晶圆上。化学气相沉积(CVD)是一种气体反应在晶圆上形成固体薄膜的过程,用于创建绝缘(介电)层。物理气相沉积(PVD),或溅射,用离子轰击靶材,使原子脱落,然后沉积到晶圆上,常用于金属层。

步骤4:掺杂(改变导电性)

为了使晶体管工作,硅本身的电学性能必须被修改。这通过离子注入完成,这是一个高能粒子加速器将特定离子(如硼或磷)射入硅晶圆的过程。这种“掺杂”产生了负型(N型)和正型(P型)区域,使晶体管能够开关。

光刻、刻蚀、沉积和掺杂的这个循环重复数百次,以构建现代晶体管的复杂三维结构。

连接晶体管:后端工艺 (BEOL)

一旦在FEOL阶段形成了数十亿个晶体管,它们就必须被连接起来。这种“布线”,称为互连,是在晶体管之上构建的由铜或铝路径组成的密集多层网格。

金属化工艺

BEOL工艺与FEOL非常相似,但侧重于创建导电路径而不是晶体管。沉积一层绝缘材料,然后使用光刻和刻蚀来创建沟槽和通孔(垂直连接),这些地方将是导线所在的位置。

构建布线层

然后通过称为大马士革工艺的过程将这些沟槽填充铜。表面多余的铜被抛光掉,留下一个完全平坦的层,其中嵌有铜布线。这个过程重复进行,以构建一个由10-20层布线组成的复杂“高速公路系统”,将所有单个晶体管连接成一个功能电路。

理解权衡和挑战

半导体制造过程以其极端的挑战而闻名。成功取决于克服这些挑战的能力。

洁净度的苛刻要求

现代晶体管如此之小,以至于一粒灰尘就像一块巨大的巨石,能够使电路短路并毁坏整个芯片。这就是为什么芯片是在洁净室中制造的,这些设施比手术室洁净数千倍。工人必须穿着从头到脚的“无尘服”以防止污染。

追求更小的节点

行业的发展是由晶体管小型化推动的,这一趋势由摩尔定律描述。这些“工艺节点”(例如,7纳米,5纳米)指的是芯片上特征的尺寸。随着特征尺寸的缩小,量子隧穿等物理挑战(电子穿透绝缘体泄漏)变得显著,需要新的材料和晶体管设计(如FinFET)。

良率:成功的最终衡量标准

良率是每片晶圆上合格芯片的百分比。由于该过程有数百个步骤,任何阶段的微小错误都可能产生缺陷。90%的良率听起来可能很高,但这意味着10%的极其昂贵的生产是无用的。即使提高1-2%的良率,也可能带来数百万美元的额外收入。

芯片的最终完成:组装和测试

经过数百个步骤后,晶圆上承载着数百或数千个独立的芯片,称为裸片。

晶圆测试和切割

首先,自动化探针测试晶圆上的每个独立裸片,以识别哪些是功能正常的。然后,通过称为切割的过程,用金刚石锯将晶圆切割成独立的裸片。

封装和最终测试

然后将功能正常的裸片送去封装。微小而脆弱的硅裸片被安装到基板上,并封装在保护性的塑料或陶瓷外壳中。这个封装提供了连接芯片与外部世界的金属引脚或焊盘。封装后,芯片在出货前会进行最终的严格测试。

为什么这个过程很重要

了解芯片制造的基本原理为整个技术领域提供了重要的背景信息。

- 如果您的主要关注点是工程或研究: 认识到光刻、刻蚀、沉积和掺杂的迭代循环是所有现代电子产品的基本组成部分。

- 如果您的主要关注点是商业或投资: 理解良率、晶圆厂(fab)巨大的资本成本以及不断追求更小工艺节点的竞赛是市场竞争和供应链动态的主要驱动因素。

- 如果您的主要关注点是普遍技术: 欣赏您手中的智能手机或云中运行的服务器是人类有史以来开发的最复杂、最精确、最昂贵的制造过程之一的成果。

最终,数字世界不仅建立在巧妙的软件之上,而且建立在应用物理和制造精度在几乎无法想象的规模上的物理基础之上。

总结表:

| 阶段 | 关键工艺 | 目的 |

|---|---|---|

| 晶圆制造 | 晶体生长和抛光 | 创建超纯硅基底 |

| 前端工艺 (FEOL) | 光刻、刻蚀、沉积、掺杂 | 构建数十亿个晶体管 |

| 后端工艺 (BEOL) | 金属化和大马士革工艺 | 用金属层将晶体管连接起来 |

| 组装和测试 | 切割、封装、最终测试 | 准备单个芯片以供使用 |

准备好为半导体研究或生产配备您的实验室了吗? KINTEK专注于半导体制造过程中必不可少的高精度实验室设备和耗材,包括沉积系统、刻蚀工具和晶圆处理解决方案。我们的专业知识确保您的工作所需的可靠性和纯度。立即联系我们的专家,讨论我们如何支持您的实验室在半导体行业的特定需求。

图解指南

相关产品

- 光学窗口玻璃基板晶圆石英片 JGS1 JGS2 JGS3

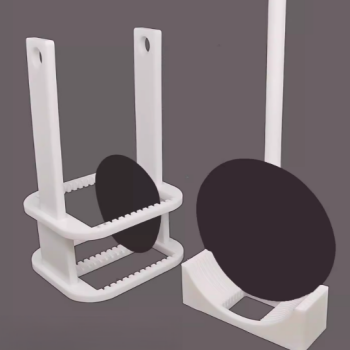

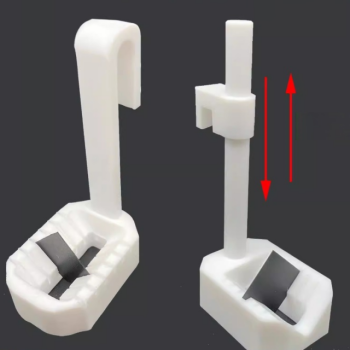

- 半导体和实验室应用的定制PTFE晶圆载具

- 适用于半导体和医疗晶圆加工的多功能PTFE解决方案

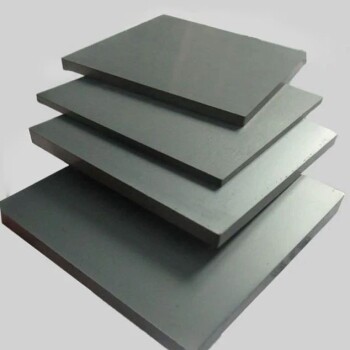

- 碳化硅(SiC)陶瓷板 耐磨工程高级特种陶瓷

- 实验室和半导体加工用定制PTFE晶圆夹具