沉积均匀性是决定半导体器件能否正常工作以及能否可靠制造的基础指标。它之所以关键,是因为薄膜厚度的变化会直接改变栅极氧化层等有源器件的电气特性,并导致蚀刻等后续工艺步骤出现严重故障。

均匀性不仅仅是质量检查;它是工艺集成的结构先决条件。均匀性差会损害关键层中的电气完整性,并扰乱后续制造步骤的时序机制。

对器件性能的直接影响

关键有源层

在器件运行中起积极作用的薄膜需要最高级别的精度。栅极氧化层或电容器层等组件依赖于特定的厚度来保持一致的电容和电压处理能力。

如果这些层的均匀性发生变化,器件的电气特性就会变得不可预测。这会导致晶圆上的性能出现差异,可能导致芯片无法使用。

非关键层容差

并非所有薄膜都需要相同的严格度。起到被动作用的层,例如封装层,通常具有更宽的工艺窗口。

虽然这些层对轻微的厚度变化不太敏感,但了解区别可以让制造商将资源优先用于最重要的地方。

制造和工艺集成

对生产的连锁反应

沉积阶段缺乏均匀性并非孤立存在;它会对后续步骤产生负面影响。最显著的冲突发生在蚀刻过程中。

蚀刻挑战

蚀刻工艺是根据特定的薄膜厚度进行计时。如果薄膜的厚度均匀性差,最厚区域所需的蚀刻时间将与最薄区域不同。

这就造成了一个两难境地:如果蚀刻时间足够长以清除最厚的区域,可能会损坏最薄区域下方的基板。反之,如果过早停止以保护最薄的区域,最厚的区域将留下残留材料,导致电气短路或开路。

理解权衡

平衡精度与效率

虽然高均匀性通常是可取的,但在每个层面上都追求完美可能效率低下。对非关键薄膜过度追求严格的规格通常会带来不必要的成本并降低吞吐量,而不会为最终产品增加价值。

过度规格化的风险

工程师必须确定哪些层真正驱动良率。对封装层的均匀性过度设计会分散对关键有源层的注意力,而这些层中的厚度变化是真正的失效模式。

优化您的均匀性策略

为了确保高良率和可靠的性能,您必须将均匀性规格与薄膜的具体功能相匹配。

- 如果您的主要重点是关键器件运行:优先对栅极氧化层和电容器层进行严格的均匀性控制,以确保一致的电气行为。

- 如果您的主要重点是工艺集成:确保足够的厚度均匀性,以防止在后续的图案化步骤中出现蚀刻不足或过度蚀刻。

真正的工艺控制来自于理解您的器件可以容忍哪些变化,哪些变化会破坏您的制造流程。

摘要表:

| 因素 | 对制造的影响 | 均匀性差的后果 |

|---|---|---|

| 电气特性 | 影响栅极氧化层和电容器 | 不可预测的电压和性能故障 |

| 蚀刻工艺 | 扰乱定时蚀刻周期 | 过度蚀刻损坏或残留材料短路 |

| 工艺集成 | 影响下游兼容性 | 缺陷增加,晶圆良率降低 |

| 成本管理 | 资源分配策略 | 过度规格化导致吞吐量降低 |

使用 KINTEK 提升您的薄膜精度

实现沉积均匀性和工艺效率的完美平衡对于高良率的半导体制造至关重要。在 KINTEK,我们深知,无论您是开发关键的栅极氧化层还是坚固的封装层,合适的设备都能带来巨大的差异。

从高性能的 CVD 和 PECVD 系统到我们先进的高温炉和真空解决方案,KINTEK 提供确保薄膜厚度一致和卓越电气完整性所需的专用工具。我们的全面产品组合——包括 MPCVD 系统、破碎和研磨设备以及精密液压机——旨在支持最苛刻的实验室和生产环境中的研究人员和制造商。

准备好优化您的制造流程并减少失效模式了吗? 立即联系 KINTEK,讨论您的设备需求和技术规格。

相关产品

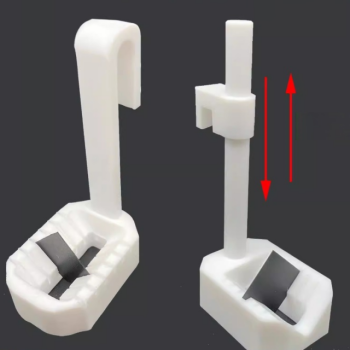

- 实验室和半导体加工用定制PTFE晶圆夹具

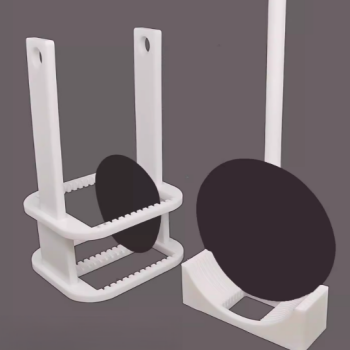

- 精密应用的CVD金刚石修整工具

- 化学气相沉积 CVD 设备系统 腔体滑动式 PECVD 管式炉 带液体汽化器 PECVD 机

- 电子束蒸发镀膜无氧铜坩埚和蒸发舟

- RF PECVD 系统 射频等离子体增强化学气相沉积 RF PECVD