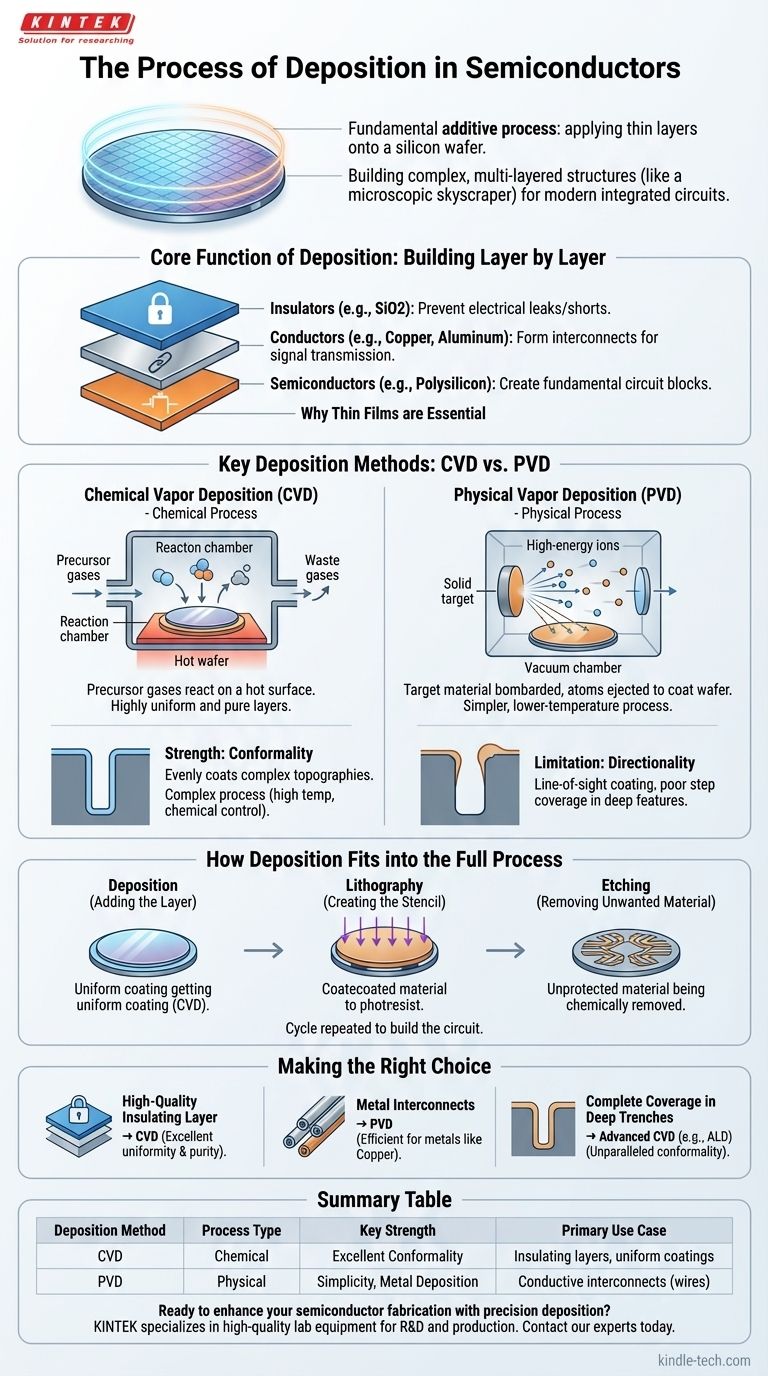

在半导体制造中,沉积是将薄层材料涂覆到硅晶圆上的基本过程。这是一个纯粹的添加过程,其中绝缘体、导体或半导体等材料被生长或涂覆在晶圆表面,通常一次只有几个原子层。它是构建形成现代集成电路的复杂多层结构的主要方法。

需要理解的关键概念是,沉积是关于在晶圆上添加一层均匀的材料。这与光刻(对层进行图案化)和刻蚀(选择性地去除层的一部分)不同,后者是制造序列中单独的后续步骤。

沉积的核心功能

逐层构建电路

将微处理器想象成一座微型多层摩天大楼。沉积就是添加每一层新楼层(绝缘层)或墙壁内的布线(导电层)的过程。

这个过程重复数百次,以构建现代芯片复杂的垂直结构。每个沉积层的质量和精度对最终设备的性能至关重要。

为什么薄膜必不可少

通过沉积形成的薄膜具有特定的关键功能:

- 绝缘体(例如,二氧化硅、氮化硅)可防止电流在不同组件之间泄漏或短路。

- 导体(例如,铜、铝、钨)形成微观导线或“互连线”,用于在晶体管之间传输信号。

- 半导体(例如,多晶硅)用于创建电路的基本构建块,例如晶体管栅极。

关键沉积方法:CVD 与 PVD

虽然有许多具体的技术,但几乎所有沉积过程都属于两大类:化学气相沉积(CVD)和物理气相沉积(PVD)。

化学气相沉积 (CVD)

CVD 是一种化学过程。前体气体被引入含有加热晶圆的反应室。

这些气体在热表面发生反应,留下所需材料的固体薄膜并释放其他气态副产品,然后将其排出。这种方法以生产高度均匀和纯净的层而闻名。

物理气相沉积 (PVD)

PVD 是一种物理过程,通常被比作原子级喷漆。在真空室中,固体源材料(称为“靶材”)受到高能离子的轰击。

这种轰击将原子从靶材上撞击下来。这些原子随后穿过真空并涂覆在晶圆上,逐个原子地构建薄膜。

理解权衡

CVD 和 PVD 之间的选择取决于所沉积的材料和层的结构要求。

CVD:共形性与复杂性

CVD 的优势在于其共形性。由于化学反应在表面各处发生,它可以均匀地涂覆晶圆地形中非常深、窄的沟槽的底部和侧面。

权衡是复杂性。CVD 通常需要高温,并涉及挥发性化学反应,必须精确控制以确保层的纯度并防止缺陷。

PVD:简单性与方向性

PVD 通常是一种更简单、低温的过程,非常适合沉积无法承受 CVD 高温的金属。

其主要限制是方向性。由于原子从靶材到晶圆是“视线”传播的,PVD 难以均匀涂覆深层特征的侧壁,这个问题被称为“台阶覆盖”不良。

沉积如何融入整个过程

一些制造指南中描述的步骤可能令人困惑。沉积只是重复循环的三个步骤中的第一部分。

步骤 1:沉积(添加层)

使用 CVD 等方法,将一层均匀的材料(例如氮化硅)沉积在晶圆的整个表面上。

步骤 2:光刻(创建模板)

将一层光敏材料(称为光刻胶)涂覆在沉积层顶部。然后通过图案化掩模将其暴露在紫外线下,并显影图案,从而形成保护性模板。

步骤 3:刻蚀(去除不需要的材料)

化学或等离子体刻蚀工艺去除未受光刻胶模板保护区域的氮化硅。最后,去除剩余的光刻胶,留下所需的电路图案。

为您的目标做出正确选择

沉积方法的选择完全取决于集成电路中特定层的功能。

- 如果您的主要重点是创建高质量的绝缘层(例如,晶体管栅氧化层):化学气相沉积(CVD)是首选方法,因为它具有出色的均匀性和纯度。

- 如果您的主要重点是创建金属互连线(导线):物理气相沉积(PVD)通常用于高效沉积铜或铝等金属。

- 如果您的主要重点是确保深窄沟槽中的完全覆盖:需要原子层沉积(ALD)等先进技术,这是一种精确的 CVD 子类型,具有无与伦比的共形性。

最终,掌握沉积就是要选择正确的添加技术,为每个后续的图案化和刻蚀步骤精确构建基础。

总结表:

| 沉积方法 | 工艺类型 | 主要优势 | 主要应用场景 |

|---|---|---|---|

| 化学气相沉积 (CVD) | 化学 | 出色的共形性 | 绝缘层,均匀涂层 |

| 物理气相沉积 (PVD) | 物理 | 简单性,金属沉积 | 导电互连线(导线) |

准备好通过精密沉积来增强您的半导体制造工艺了吗?KINTEK 专注于为半导体研发和生产提供高质量的实验室设备和耗材。无论您需要用于均匀绝缘层的 CVD 系统,还是用于可靠金属互连的 PVD 工具,我们的解决方案都旨在满足现代芯片制造的严格要求。立即联系我们的专家,讨论我们如何支持您实验室的特定沉积需求,并帮助您构建更好的集成电路。

图解指南