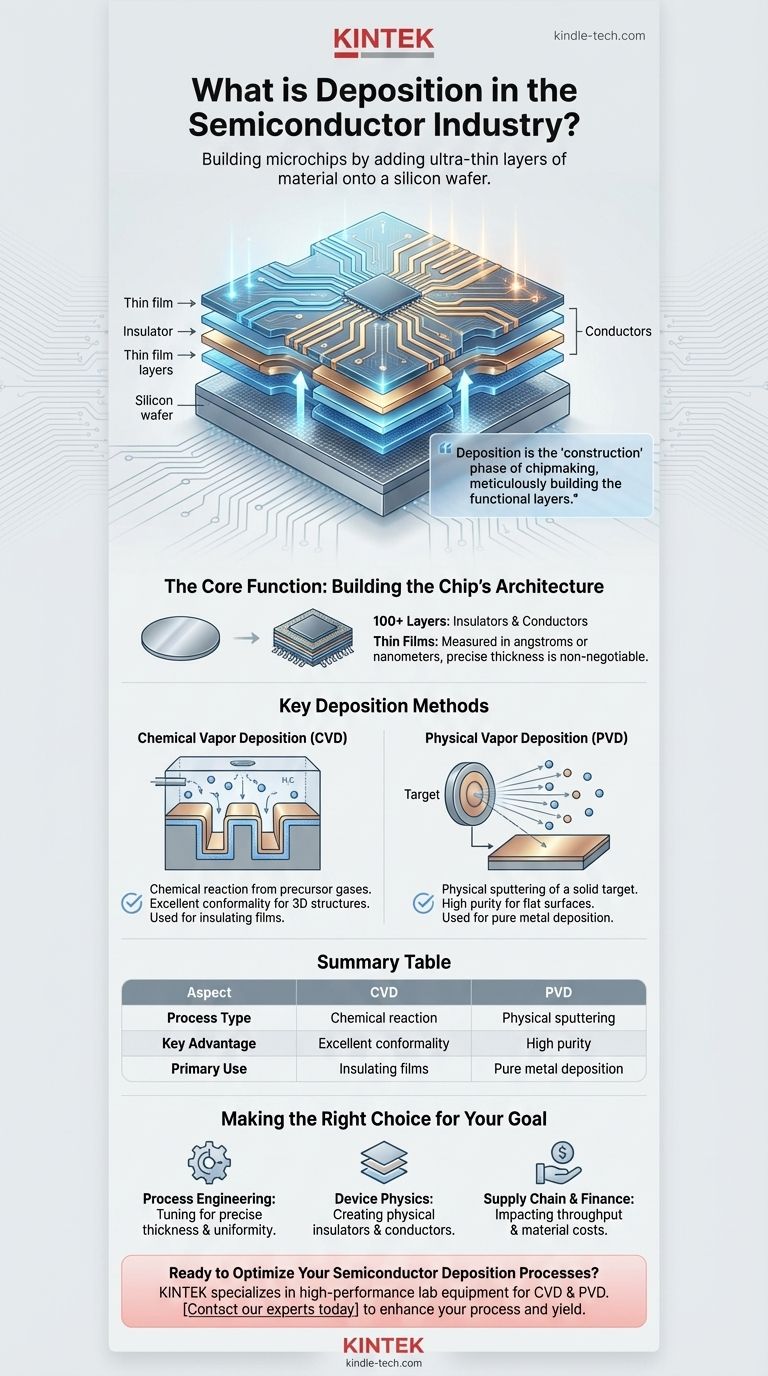

在半导体制造中,沉积是构建微芯片的基本过程,它通过在硅晶圆上添加超薄的材料层来实现。这种受控的原子或分子薄膜的添加,形成了构成芯片复杂电路所必需的绝缘和导电结构。

需要掌握的核心原则是,沉积是芯片制造的“构建”阶段。当其他步骤绘制蓝图(光刻)或去除材料(刻蚀)时,沉积是负责精心构建集成电路功能层的过程。

核心功能:构建芯片的架构

沉积不仅仅是表面涂层;它是一系列高度精确的工程步骤,将空白的硅晶圆转变为多层电子器件。

从裸硅到复杂电路

成品微处理器可以在彼此堆叠的材料层数超过100层。沉积是负责创建所有这些层的过程。

这包括添加绝缘层(如二氧化硅)以防止电流泄漏,以及添加导电层(如铜或钨)以形成传输信号的导线和晶体管。

薄膜的概念

沉积过程中添加的层被称为薄膜。它们的厚度以埃或纳米为单位测量,通常只有几十到几百个原子厚。

每层薄膜的精确厚度、纯度和结构质量都是不可妥协的。即使是微小的偏差也会极大地改变最终器件的电气特性,使整个芯片报废。

关键的沉积方法

沉积方法的选择完全取决于所沉积的材料及其在芯片架构中的用途。最基本的两大类是化学气相沉积和物理气相沉积。

化学气相沉积 (CVD)

CVD是最广泛使用的沉积技术。它的工作原理是将一种或多种前驱气体引入含有硅晶圆的反应室中。

这些气体发生化学反应,该反应的固体副产物作为均匀的薄膜“沉积”在晶圆表面上。可以将其视为一个受控的化学反应,其中固体产物在芯片上形成新的一层。

CVD对于创建高质量的绝缘薄膜和各种金属层至关重要。

物理气相沉积 (PVD)

相比之下,PVD是一个机械或机电过程。在一种常见的PVD技术——“溅射”中,目标材料的固体靶材受到高能离子的轰击。

这种轰击将原子从靶材上击落,然后这些原子穿过真空并覆盖在晶圆上。可以将其想象成一种原子级别的喷漆。PVD非常适合沉积纯金属。

理解权衡

没有哪种方法是普遍优越的;它们是根据芯片设计所呈现出的特定几何和材料挑战来选择的。

CVD的优势:保形性

CVD的主要优势在于其出色的保形性(Conformality)。由于沉积来自反应性气体,它可以均匀地覆盖复杂三维结构的所有表面,包括深槽的底部和侧壁。

PVD的优势:视线

PVD是一个视线(Line-of-Sight)过程。溅射出的原子以相对直线的路径传播,这使得很难均匀覆盖深槽的垂直侧壁。它的优势在于在相对平坦的表面上沉积非常纯净的材料。

选择取决于层的功用

工程师根据需求选择方法。要在深而窄的晶体管栅极内部创建完美的绝缘屏障,需要CVD卓越的保形性。要在相对平坦的平面上铺设主要的金属互连线,PVD的速度和纯度可能是最佳选择。

为您的目标做出正确的选择

您如何看待沉积,取决于您在半导体生态系统中的角色。了解其功能是理解整个制造流程的关键。

- 如果您的主要重点是工艺工程: 您的挑战是选择和调整正确的沉积方法(CVD、PVD、ALD等),以实现特定层所需的精确薄膜厚度、均匀性和材料特性。

- 如果您的主要重点是器件物理学: 您将沉积视为创造物理绝缘体和导体的工具,它们的特性直接决定了晶体管的电气性能和可靠性。

- 如果您的主要重点是供应链或财务: 沉积代表着主要的资本和运营支出,其中技术选择直接影响工厂的吞吐量、材料成本和设备正常运行时间。

最终,理解沉积就是理解现代微芯片是如何从原子层面构建起来的。

总结表:

| 方面 | 化学气相沉积 (CVD) | 物理气相沉积 (PVD) |

|---|---|---|

| 工艺类型 | 前驱气体发生的化学反应 | 固体靶材的物理溅射 |

| 主要优势 | 对3D结构具有出色的保形性 | 对平坦表面具有高纯度 |

| 主要用途 | 绝缘薄膜、复杂的金属层 | 纯金属沉积 |

准备优化您的半导体沉积工艺?

KINTEK 专注于为半导体研发和制造提供高性能的实验室设备和耗材。无论您是开发下一代CVD技术,还是需要可靠的PVD解决方案,我们的专业知识都能确保您实现对微芯片至关重要的精确薄膜厚度、均匀性和材料纯度。

立即通过我们的联系表单联系我们的专家,讨论我们的定制化解决方案如何增强您的沉积工艺、提高良率并加速您的产品上市时间。

图解指南

相关产品

- 化学气相沉积 CVD 设备系统 腔体滑动式 PECVD 管式炉 带液体汽化器 PECVD 机

- 915MHz MPCVD金刚石设备 微波等离子体化学气相沉积系统反应器

- 客户定制多功能CVD管式炉化学气相沉积腔体系统设备

- HFCVD设备用于拉丝模具纳米金刚石涂层

- 分体式真空站化学气相沉积系统设备管式炉