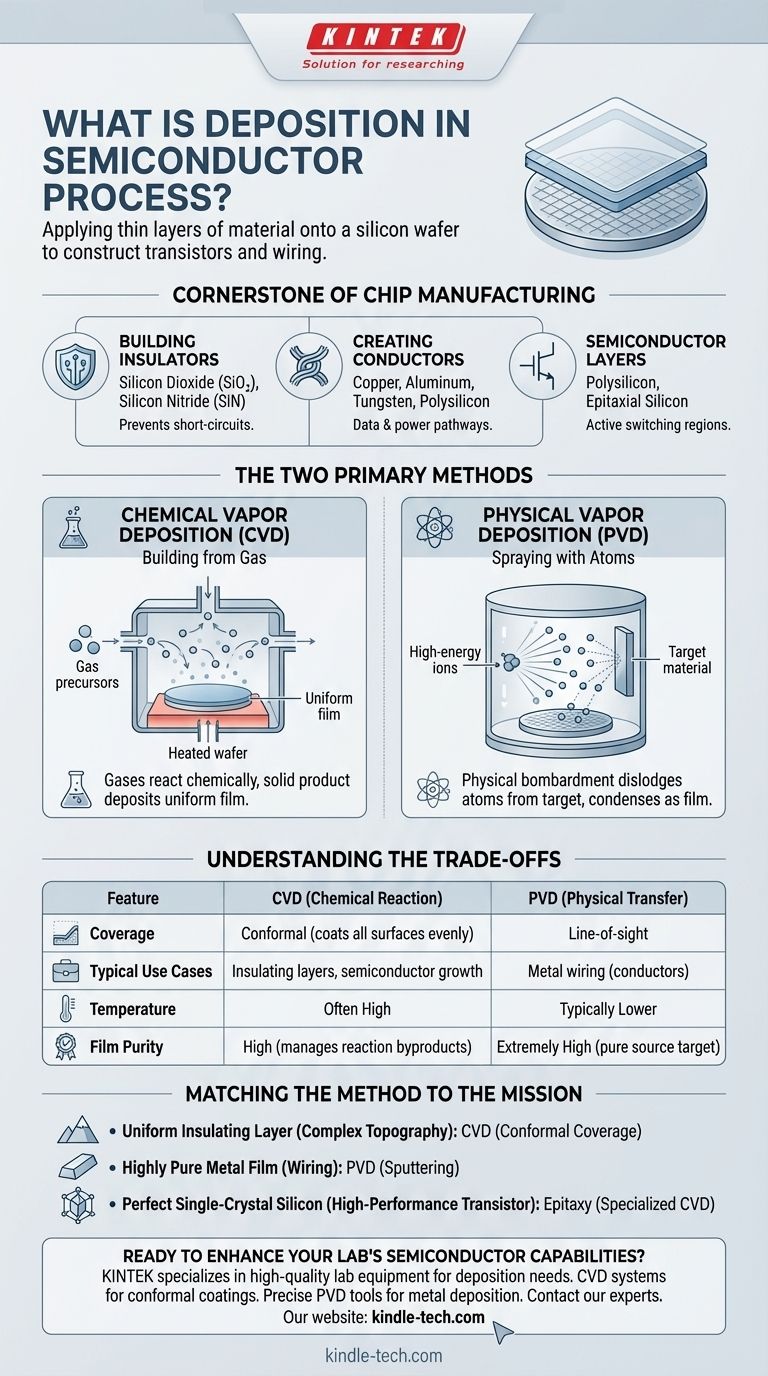

简而言之,沉积是将薄层材料沉积到硅晶圆上的过程。这些经过精确控制的薄膜,通常只有几个原子厚,是用于构建构成晶体管及其连接线路的复杂三维结构的基本构件。

沉积的核心目的不仅仅是添加层,而是精确地构建集成电路的基本组成部分——导体、绝缘体和半导体——使其能够正常工作。

为什么沉积是芯片制造的基石

每块微芯片都是一个由数十亿微小组件构成的复杂“城市”。沉积就是逐层构建这个城市结构的过程。

构建绝缘体

绝缘薄膜,通常由二氧化硅 (SiO₂) 或氮化硅 (SiN) 等材料制成,至关重要。它们充当屏障,防止电流在不同的导电路径之间泄漏或“短路”。

创建导体

导电薄膜构成了芯片的“导线”和“栅极”。沉积铜、铝、钨和多晶硅等材料,以创建允许电流流动的通路,在整个电路中传输数据和电力。

铺设半导体层

专业的沉积工艺用于生长或放置半导体材料层,如多晶硅或外延硅。这些是晶体管开关动作发生的“活性”区域。

沉积的两种主要方法

尽管有许多专业技术,但几乎所有的沉积都属于两大主要类别:化学气相沉积 (CVD) 和物理气相沉积 (PVD)。选择哪种方法完全取决于要沉积的材料和要构建的结构。

化学气相沉积 (CVD):从气体构建

CVD 是最常见的方法。它涉及将一种或多种气体(前驱体)引入含有晶圆的反应室中。

这些气体发生化学反应,反应产生的固体产物“沉积”在晶圆表面,形成均匀的薄膜。可以将其想象成空气中通过化学反应形成的精确控制的霜。

物理气相沉积 (PVD):用原子喷涂

PVD 是一种物理过程,而非化学过程。它的工作原理是在真空中用高能离子轰击固体源材料(“靶材”)。

这种轰击会将原子从靶材上撞击下来,然后这些原子会迁移并凝结在较冷的晶圆上,形成薄膜。这类似于原子级别的喷漆过程。

理解权衡:CVD 与 PVD

没有哪种方法是普遍更好的;它们是用于不同任务的工具,每种方法都有明显的优点和缺点。

保形覆盖与视线

CVD 擅长创建保形层。由于薄膜是由气体反应形成的,它可以均匀地覆盖复杂三维沟槽或结构的所有表面。

PVD 是一个视线过程。就像喷漆罐一样,它会覆盖它能“看到”的表面,因此很难均匀地覆盖深沟槽的底部和侧壁。

薄膜质量和纯度

PVD 可以产生极其纯净的薄膜,因为源材料本身通常非常纯净。这使其成为沉积对纯度要求极高的金属互连的理想选择。

CVD 薄膜的性能在很大程度上取决于化学反应、温度和压力。虽然高质量的薄膜是常规的,但管理反应产生的副产物是一个关键考虑因素。

材料和温度限制

CVD 工艺通常需要非常高的温度来驱动化学反应。如果高温可能会损坏晶圆上已经构建的层,这就会成为一个问题。

PVD 通常可以在较低的温度下进行,因此适用于芯片更敏感的制造后期步骤。

将方法与任务相匹配

选择正确的沉积技术对于实现芯片每个部分所需的所需电气和结构特性至关重要。

- 如果您的主要重点是在复杂地形上创建均匀的绝缘层: 由于其出色的保形覆盖能力,CVD 是明确的选择。

- 如果您的主要重点是沉积用于布线的超纯金属薄膜: PVD(特别是称为溅射的技术)是该任务的行业标准。

- 如果您的主要重点是生长完美的单晶硅层以用于高性能晶体管: 需要一种称为外延生长的专业 CVD 技术。

最终,沉积通过原子级层的有意和精确的构建,将空白的硅晶圆转变为正常工作的集成电路。

摘要表:

| 特征 | 化学气相沉积 (CVD) | 物理气相沉积 (PVD) |

|---|---|---|

| 工艺类型 | 来自气体的化学反应 | 原子的物理转移 |

| 覆盖范围 | 保形(均匀覆盖所有表面) | 视线 |

| 典型用例 | 绝缘层,半导体生长 | 金属布线(导体) |

| 温度 | 通常较高 | 通常较低 |

| 薄膜纯度 | 高(管理反应副产物) | 极高(纯源靶材) |

准备好提升您实验室的半导体研究或生产能力了吗? KINTEK 专注于为您所有沉积工艺需求提供高质量的实验室设备和耗材。无论您需要用于保形涂层的可靠 CVD 系统,还是用于金属沉积的精确 PVD 工具,我们的解决方案都旨在满足现代半导体制造的严格要求。立即联系我们的专家,讨论我们如何支持您实验室的成功。

图解指南