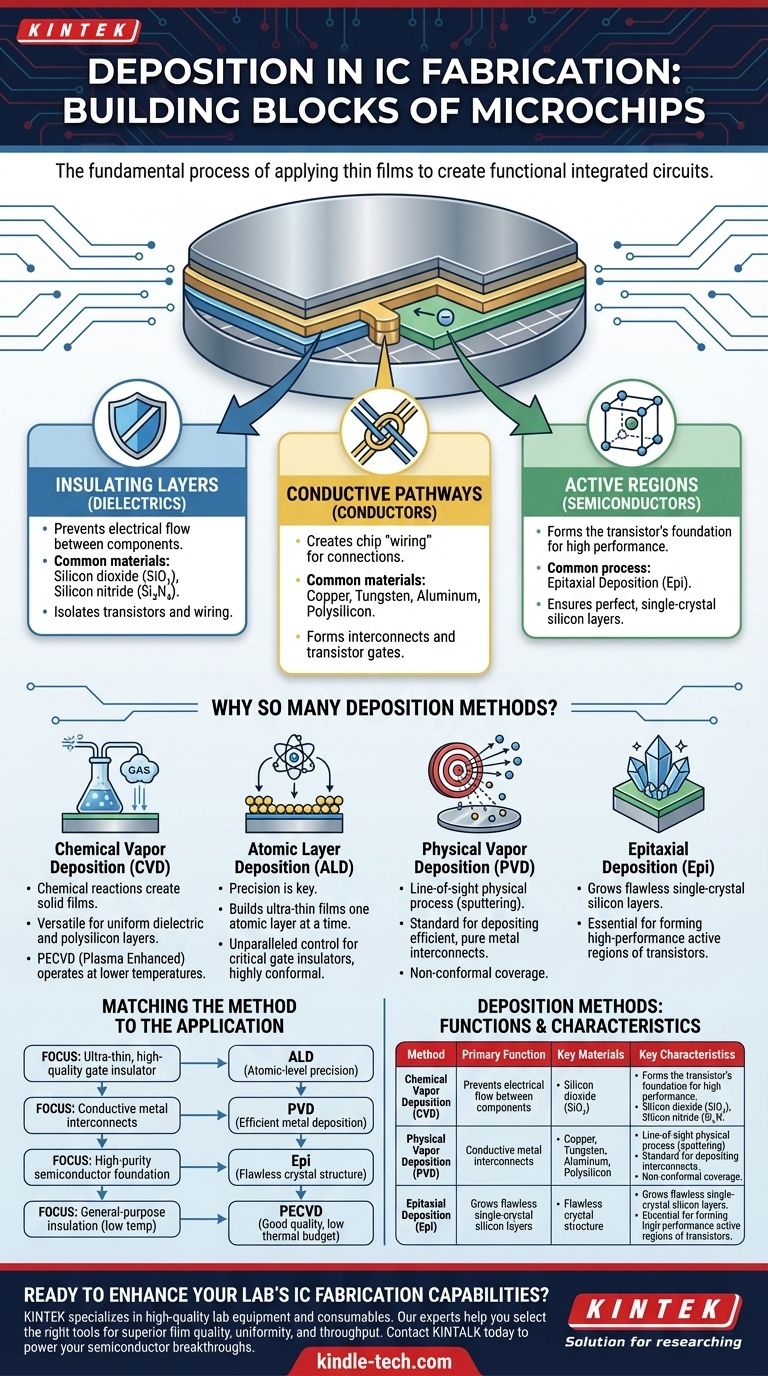

在集成电路(IC)制造中,沉积是用于在硅晶圆上应用各种材料薄膜的基本过程。这些经过精确控制的层不仅仅是涂层;它们是创建微芯片功能组件的基本构件,充当形成每个晶体管和导线的导体、绝缘体和半导体。

沉积的核心目的是精确构建IC复杂的三维结构。它是制造过程中的“增材”部分,其中每一层沉积物都服务于特定的电气或结构功能,使得数十亿微小组件能够协同工作。

沉积层的核心功能

沉积的根本在于添加材料,这些材料在电路中扮演三个关键角色。添加每一层都是为了一个特定的目的,以确保最终器件能够正常工作。

创建绝缘层(电介质)

要构建一个功能性电路,必须防止电流流向错误的位置。沉积用于添加绝缘材料,也称为电介质,如二氧化硅(SiO₂)和氮化硅(Si₃N₄)。

这些层将导电元件彼此隔离,防止短路。例如,电介质薄膜将晶体管的栅极与其下方的沟道隔离开来,并分离连接芯片不同部分的多个金属布线层。

形成导电通路(导体)

晶体管构建完成后,必须将它们连接起来。沉积用于通过沉积导电材料来创建芯片的“布线”或互连线。

铜、钨和铝等金属是常见的选择。此过程还包括沉积多晶硅(polysilicon),这对于形成晶体管的栅极至关重要——栅极是控制其开启和关闭的组件。

构建有源区(半导体)

晶体管的性能取决于其所构建的硅的质量。一种称为外延沉积(Epi)的工艺用于在起始晶圆上生长一层完美的单晶硅。

这层无瑕的、没有杂质和缺陷的材料成为晶体管运行的有源区,确保了最佳的电气特性和高性能。

为什么有这么多沉积方法?

从CVD到PVD再到ALD,存在各种沉积技术,因为没有一种方法对所有应用都是完美的。选择何种技术取决于所沉积的材料、所需的薄膜质量以及晶圆上现有结构的温度敏感性。

化学气相沉积(CVD)

CVD包含一系列技术(LPCVD、PECVD、APCVD),它们利用前驱体气体之间的化学反应在晶圆表面形成固体薄膜。

这种方法用途广泛,是制造高质量、均匀的电介质层和多晶硅层的“主力军”。等离子体增强化学气相沉积(PECVD)尤其有价值,因为它可以在较低的温度下运行,从而防止损坏先前构建的层。

原子层沉积(ALD)

对于最关键的组件,例如现代晶体管中超薄的栅极绝缘体,精度至关重要。原子层沉积(ALD)通过一次只构建一个原子层的薄膜来实现这一点。

虽然比其他方法慢,但ALD在厚度和均匀性方面提供了无与伦比的控制,这在器件特征缩小到纳米级时是绝对必要的。

物理气相沉积(PVD)

与CVD的化学反应不同,物理气相沉积(PVD)是一个视线物理过程,通常称为溅射。在PVD中,靶材受到离子轰击,将原子溅射出来,然后这些原子落在晶圆表面并覆盖其上。

PVD是沉积用作互连线的金属层的标准方法,因为它是一种可靠且高效的方式来沉积纯金属薄膜。

理解权衡

选择沉积方法总是在相互竞争的要求之间进行权衡。工程师必须考虑结构的几何形状、器件的热限制以及所需薄膜的质量。

保形覆盖与非保形覆盖

一些工艺,如ALD和LPCVD,会产生高度保形的薄膜,这意味着它们以完全均匀的厚度覆盖复杂3D结构的顶部、侧面和底部。

相比之下,PVD是一个视线过程,是非保形的。它可能难以均匀地覆盖深而窄的沟槽的底部和侧壁,这对某些应用来说是一个限制。

热预算限制

每个工艺步骤都有一个热预算——即晶圆可以承受而不损坏已制造结构的温度和时间限制。

LPCVD等高温工艺必须在制造流程的早期使用。后续步骤则依赖于PECVD和PVD等低温方法,以避免破坏其下方的精细晶体管结构。

薄膜质量与吞吐量

沉积薄膜的完美程度与工艺速度之间通常存在直接的权衡。

ALD产生的薄膜近乎完美,但速度非常慢,因此只适用于最关键、最薄的层。相反,其他方法可能以略低的薄膜质量为代价提供更高的吞吐量(每小时处理更多晶圆),但这对于不太关键的层是可以接受的。

将方法与应用相匹配

选择正确的沉积技术取决于所创建层的具体功能。

- 如果您的主要重点是超薄、高质量的栅极绝缘体: 原子层沉积(ALD)是必需的选择,因为它具有原子级的精度。

- 如果您的主要重点是沉积导电金属互连线: 物理气相沉积(PVD)是标准的主力,因为它在金属沉积方面效率高。

- 如果您的主要重点是高纯度半导体基础: 使用外延沉积(Epi)来创建高性能晶体管所需无瑕的晶体结构。

- 如果您的主要重点是金属层之间的通用绝缘: 等离子体增强化学气相沉积(PECVD)常被使用,因为它在制造友好的低温下具有良好的质量。

归根结底,沉积是IC制造的主导工艺,它实现了精确的逐层构建,将简单的硅晶圆转变为强大的处理器。

摘要表:

| 沉积方法 | 主要功能 | 关键材料 | 关键特性 |

|---|---|---|---|

| 化学气相沉积 (CVD) | 电介质和多晶硅层 | SiO₂, Si₃N₄, 多晶硅 | 多功能,均匀薄膜 |

| 等离子体增强CVD (PECVD) | 低温绝缘 | SiO₂, Si₃N₄ | 低热预算,良好保形性 |

| 原子层沉积 (ALD) | 超薄栅极绝缘体 | 高k电介质 | 原子级精度,高保形性 |

| 物理气相沉积 (PVD) | 金属互连线 | 铜、铝、钨 | 高效金属沉积,视线过程 |

| 外延沉积 (Epi) | 高质量半导体基底 | 单晶硅 | 用于高性能晶体管的无瑕晶体结构 |

准备好增强您实验室的IC制造能力了吗? 您的沉积过程的精度和质量对您的成功至关重要。KINTEK 专注于高质量的实验室设备和耗材,以满足您所有的沉积需求,从研究到生产。我们的专家可以帮助您选择正确的工具,以实现卓越的薄膜质量、均匀性和吞吐量。

立即联系KINTEK,讨论我们的解决方案如何为您的半导体技术突破提供动力。

图解指南